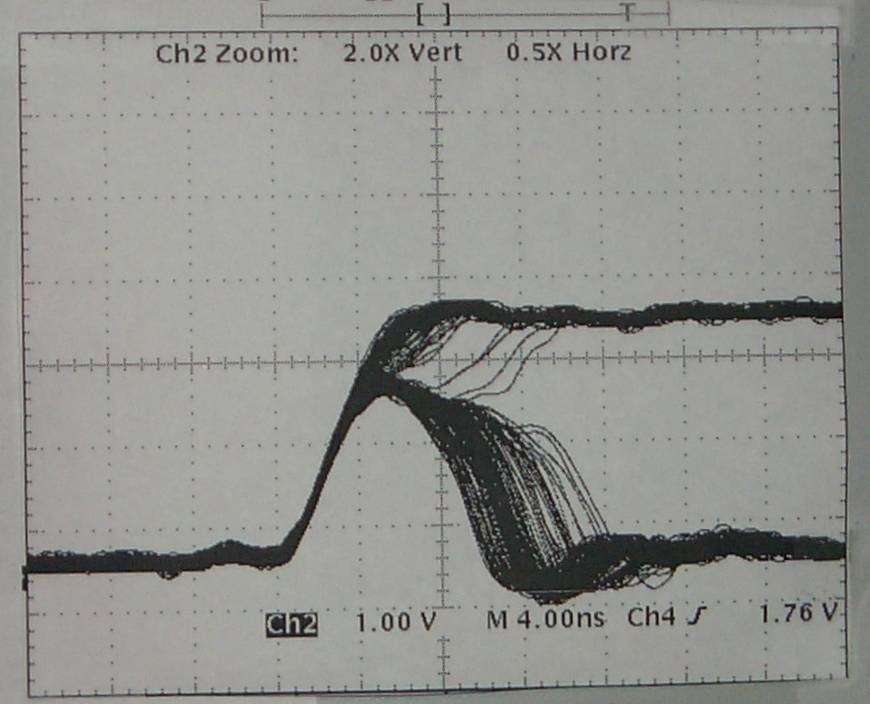

o conceito eh um pouco complexo para explicar, mas basicamente, se o sinal de entrada em um flip-flop (e os microcontroladores sao feitos com milhares deles) mudar de forma assincrona no instante do pulso de clock do flip-flop, ele entra em um estado em que nao consegue se decidir se vai comutar para 1 ou 0. a aterrorizante imagem abaixo mostra isso:

o signal de entrada provavelmente comuta de 0 para 1 exatamente na borda de clock. o resultado eh que normalmente o flip-flop comuta de 0 para 1 sua saida, porem as vezes ele vai ateh metade do caminho e volta. umas poucas vezes, como se ve no grafico, ele vai ateh a metade do caminho, fica na duvida, mas decide ir adiante. isso eh diretamente relacionado com o sinal de entrada assincrono estar um pouco mais adiantado ou atrasado em relacao a borda de clock.

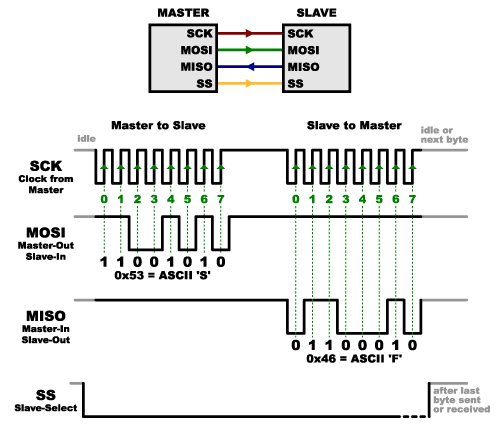

idealmente, o certo seria ele estar distante da borda de clock. isso eh didaticamente enfatizado na interface SPI, por exemplo:

neste caso, os sinais mudam em uma borda do clock (descida) e sao amostrados na borda oposta (subida), de modo que o sinal fica perfeitamente estavel durante a janela de amostragem. mas a coisa eh um pouco mais complexa do que parece: no caso do master, o clock do microcontrolador eh usado para todo o bloco da SPI, de modo que este clock eh enviado para fora e todos os sinais estao sincronizados. mas no slave a coisa eh diferente: se ele possuir clock interno, provavelmente ele vai ter que amostrar os sinais da SPI passando por flip-flops duplos ou triplos de acordo com esse clock interno:

no caso, o primeiro dominio de clock seria o master e o segundo dominio de clock seria o slave. eh facil ver que, se o sinal do master for muito rapido, o slave nao consegue amostrar corretamente: se o primeiro flip-flop falhar por meta-estabilidade, o sinal de entrada vai ser amostrado corretamente apenas no proximo clock. assim, se o sinal produzido pelo primeiro dominio for rapido demais, o segundo flip-flop do segundo dominio de clock nao pega ele! e ainda tem a possibilidade de, em condicao normal, o pulso ser curto demais pq os clocks estao com drift. assim, o pulso teria que ter largura de pelo menos 3 pulsos de clock do segundo dominio. em implementacoes boas, o pessoal coloca pelo menos 16 clocks para garantir.

assim, se vc tem dominios de clock diferentes, vc deve reduzir a taxa dos sinais, o que nesse caso seria equivalente a reduzir a velocidade da SPI. eh por isso que como master o microcontrolador consegue trabalhar com uma velocidade alta, mas como slave nao. entao, se vc for ligar dois microcontroladores, provavelmente vai ter que trabalhar com um clock SPI menor.

outra opcao para o slave seria trabalhar diretamente com o clock da SPI, sem amostrar. neste caso o clock pode ser maior, porem o slave nao pode operar em um dominio de clock proprio. essa opcao normalmente eh usada por perifericos, por exemplo, uma memoria SPI: neste caso, o clock da SPI que vem do master eh o clock da memoria, assim master e slave estao no mesmo dominio de clock e a SPI pode operar muito mais rapidamente.

a SPI eh ateh facil de resolver, mas e uma interface mais avancada?

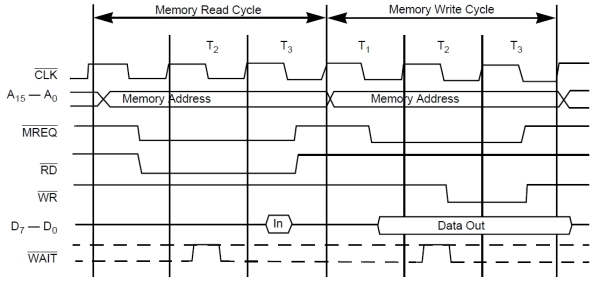

lah no colegio, quando te ensinam a mexer com o 8080 ou Z80, vc vai lembrar que o pessoal ligando o Z80 em uma SRAM de forma assincrona. em certo aspecto, vale a explicacao do master/slave da SPI: como a conexao eh assincrona, varios clocks sao necessarios para transferir um byte entre o Z80 e as memorias. para um Z80 de 4MHz, uns 3 ou 4 clocks sao usados para cada transferencia e isso gera tempos suficientes para a memoria atuar corretamente. e mesmo assim, nao era facil ajustar o sistema para operar perfeitamente em sua velocidade maxima:

no caso de um design mais avancado, utilizando SDRAM, as transferencias ocorrem com clocks de pelo menos 100MHz e uma palavra eh transferida a cada clock. isso soh eh possivel pq o processador tem uma linha de clock que sincroniza a SDRAM:

resumindo: se o microcontrolador possui entradas nao-analogicas, ele estah sujeito a meta-estabilidade. provavelmente a meta-estabilidade nao vai causar problemas internos, mas os contornos para que isso nao ocorram causam outros problemas. as vezes o cara projeta a placa sem levar isso em consideracao e bingo: problemas inexplicaveis level "monstro" surgem o tempo todo e nem os caras da fabrica do microcontrolador conseguem explicar o motivo.

mas isso eh soh a pontinha do iceberg: se vc comecar a estudar logica NMOS e CMOS, vc fica de cabelo em peh e comeca seriamente a pensar em largar tudo e ir criar galinhas! :v hahaha