Reinaldo,

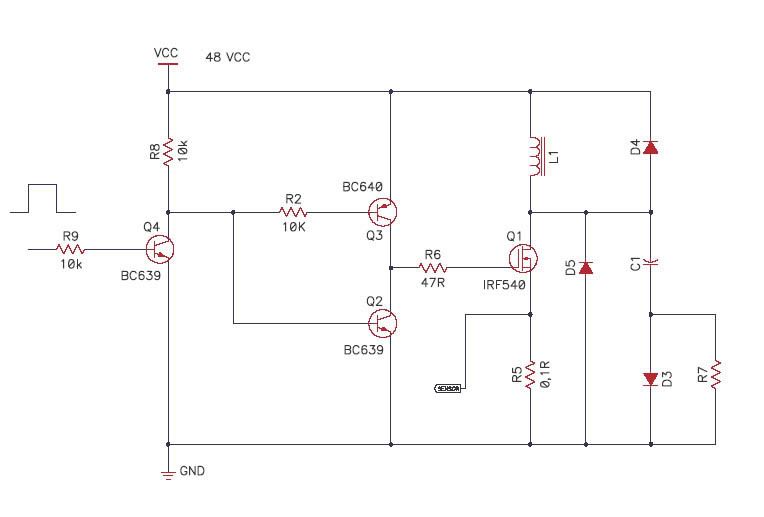

Totem, é a escultura folclórica dos indios americanos, que se constitui de várias cabeças empilhadas. Por isso o nome "Totem" quando se refere a algo 'empilhado'. No caso, apenas o estagio de driver ( BJT ) é Totem, e nao o estágio de saida ( MOSFET ), entendo eu.

Nao sei qual é a sua disponibilidade de tempo, mas quando eu estava na faculdade - e tinha tempo de sobra - eu utilizava o PSPICE para simular os circuitos sem a necessidade de perder tempo nos protótipos; A vantagem é que no simulador, não existe mal-contato

.

Tudo o que eu simulava, acontecia EXATAMENTE igual no prot-o-board, com raras excessões. Por exemplo, se eu ajustava a polarização de um BJT para 1mA, na montagem aparecia exatamente esse valor.

Bom, a respeito do seu circuito, se o chaveamento for alto, acima de 2KHz, realmente o PSPICE nao trabalha bem com simulacao de comutacao, mas vale a pena tentar.

Sobre o Inversor, esse IR2110 é usado em inversores e No-break's. Inclusuve uso num UPS que estou desenvolvendo.

Sobre o circuito, se achar algo esquizito, te escrevo.

+++