Conversor AD Delta-Sigma no PIC (AN-700)

Moderadores: andre_luis, 51, guest2003, Renie

12 mensagens

• Página 1 de 1

Conversor AD Delta-Sigma no PIC (AN-700)

Caros colegas.

Há algum tempo, resolvi compreender o "Application Note" AN-700 da Microchip. Ela trata da conversão AD utilizando um processo conhecido como Delta-Sigma.

Após muitas horas dedicadas a esta AN, acredito ter compreendido seu funcionamento.

Ora, pensei! Que maravilha! Poderei fazer aquisição de sinais analógicos com um PIC "pequeno".

O problema é que, uma vez compreendido seu funcionamento, comecei a questionar alguns detalhes. Será que o erro de conversão é realmente o apresentado? Após muitas (mais) horas de pesquisa e cálculos, infelizmente cheguei a resultados que mostravam erros de conversão bem maiores. Como supus que meus cálculos pudessem estar errados, considerei a hipótese de fazer uma conversão (também simulada em um PC) em apenas um ciclo do sinal presente na saída do comparador. Minha hipótese era que o erro cairia enormemente. E foi o que aconteceu.

O pior é que não tenho como saber se estou errado. Já tentei encontrar alguém, em diversos fóruns, para poder discutir sobre o assunto. Até agora sem resultados efetivos.

Caso alguém se interesse em discutir sobre este meu trabalho, estarei a disposição.

Caso alguém conheça algum periódico relacionado ao assunto, que possua a figura de "Revisor", agradeceria se me fosse informado.

Poderei também ser contatado pelo e-mail pzktv234@yahoo.com.br

Grato.

MOR_AL

Há algum tempo, resolvi compreender o "Application Note" AN-700 da Microchip. Ela trata da conversão AD utilizando um processo conhecido como Delta-Sigma.

Após muitas horas dedicadas a esta AN, acredito ter compreendido seu funcionamento.

Ora, pensei! Que maravilha! Poderei fazer aquisição de sinais analógicos com um PIC "pequeno".

O problema é que, uma vez compreendido seu funcionamento, comecei a questionar alguns detalhes. Será que o erro de conversão é realmente o apresentado? Após muitas (mais) horas de pesquisa e cálculos, infelizmente cheguei a resultados que mostravam erros de conversão bem maiores. Como supus que meus cálculos pudessem estar errados, considerei a hipótese de fazer uma conversão (também simulada em um PC) em apenas um ciclo do sinal presente na saída do comparador. Minha hipótese era que o erro cairia enormemente. E foi o que aconteceu.

O pior é que não tenho como saber se estou errado. Já tentei encontrar alguém, em diversos fóruns, para poder discutir sobre o assunto. Até agora sem resultados efetivos.

Caso alguém se interesse em discutir sobre este meu trabalho, estarei a disposição.

Caso alguém conheça algum periódico relacionado ao assunto, que possua a figura de "Revisor", agradeceria se me fosse informado.

Poderei também ser contatado pelo e-mail pzktv234@yahoo.com.br

Grato.

MOR_AL

Editado pela última vez por MOR_AL em 19 Out 2006 14:42, em um total de 1 vez.

-

MOR_AL - Dword

- Mensagens: 2940

- Registrado em: 19 Out 2006 09:38

- Localização: Rio de Janeiro - RJ

Re: Conversor AD Delta-Sigma no PIC (AN-700)

Dependendo da aplicação, vc nao vai conseguir bons resultados com esse tipo de conversao no PIC. Atualmente muitos PICs pequenos possuem conversao por aproximaçao sucessiva, que é bem mais preciso que o delta sigma do PIC. Talves fosse o caso de usa-los.

Vc nao terá leituras estaveis com delta sigma no PIC. Isso é devido ao fato do comparador ser um circuito analógico que esta na mesma pastilha do processador, que é digital. O comparador acaba captando muito ruido digital, o que vai tornar a leitura de tensoes baixas muito instaveis.

A tecnica de se colocar circuitos analogicos e digitais na mesma pastilha é uma coisa meio complicada e cheia de macetes que poucos fabricantes dominam. Para contornar essas dificuldades, acabam diminuindo a resoluçao do conversor para torna-lo menos sujeito a ruidos.

Por experiencia própria, percebi que a Analog Devices é o fabricante que mais tem dominio sobre essa técnica, chegando a fabricar MCUs com conversores embutidos de até 24 bits de resoluçao.

Na pratica só achei interessante o uso do delta sigma no PIC para leitura de potenciometros e sem esperar muita precisao ou estabilidade.

Eu optaria por um PIC com conversor AD dedicado que nao é muito mais caro assim.

Vc nao terá leituras estaveis com delta sigma no PIC. Isso é devido ao fato do comparador ser um circuito analógico que esta na mesma pastilha do processador, que é digital. O comparador acaba captando muito ruido digital, o que vai tornar a leitura de tensoes baixas muito instaveis.

A tecnica de se colocar circuitos analogicos e digitais na mesma pastilha é uma coisa meio complicada e cheia de macetes que poucos fabricantes dominam. Para contornar essas dificuldades, acabam diminuindo a resoluçao do conversor para torna-lo menos sujeito a ruidos.

Por experiencia própria, percebi que a Analog Devices é o fabricante que mais tem dominio sobre essa técnica, chegando a fabricar MCUs com conversores embutidos de até 24 bits de resoluçao.

Na pratica só achei interessante o uso do delta sigma no PIC para leitura de potenciometros e sem esperar muita precisao ou estabilidade.

Eu optaria por um PIC com conversor AD dedicado que nao é muito mais caro assim.

- proex

- Dword

- Mensagens: 2101

- Registrado em: 11 Out 2006 14:05

- Localização: São Paulo

Bom,

Eu me interesso por conversão Delta-Sigma, muitos conversores integrados disponíveis comercialmente (acho que todos os de alta resolução) utilizam esta técnica.

Mas realmente, integrá-la num PIC via hardware e software não produz resultados muito bons.

Se você quiser discutir as suas idéias, seria um prazer.

Até +

Eu me interesso por conversão Delta-Sigma, muitos conversores integrados disponíveis comercialmente (acho que todos os de alta resolução) utilizam esta técnica.

Mas realmente, integrá-la num PIC via hardware e software não produz resultados muito bons.

Se você quiser discutir as suas idéias, seria um prazer.

Até +

Fábio Pereira

embeddedsystems.io

embeddedsystems.io

-

Fábio Pereira - Word

- Mensagens: 674

- Registrado em: 16 Out 2006 09:07

- Localização: Kitchener, ON

Caro proex. Obrigado pelas dicas. Realmente você tem razão. Além das minhas suspeitas ainda tem que ser considerados estes fatores.

Caro Fábio. O assunto é interessante. Vislumbro duas maneiras de minimizar os erros apresentados adiante.

1- Caso fosse possível fazer uma conversão com um número inteiro de ciclos presentes na saída do comparador e que terminasse com um valor no contador de instantes monitorados (loops), que fosse fator de 2. Este sincronismo é praticamente impossível.

2- Outra possibilidade, esta menos impossível, seria fazer uma conversão com um número inteiro de ciclos e o contador de loops maior que 256. O problema é que seria necessário fazer uma divisão de números inteiros de até 16 bits (valor do registrador de número de eventos presentes no semi-ciclo negativo / valor do registrador de número de loops). Isso em um PIC com limitação de memória de programa seria difícil.

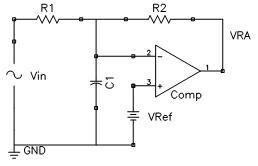

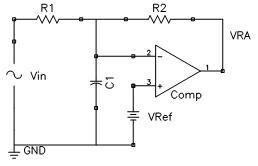

O circuito básico é mostrado na figura a seguir. Ela auxilia o acompanhamento dos fatores expostos.

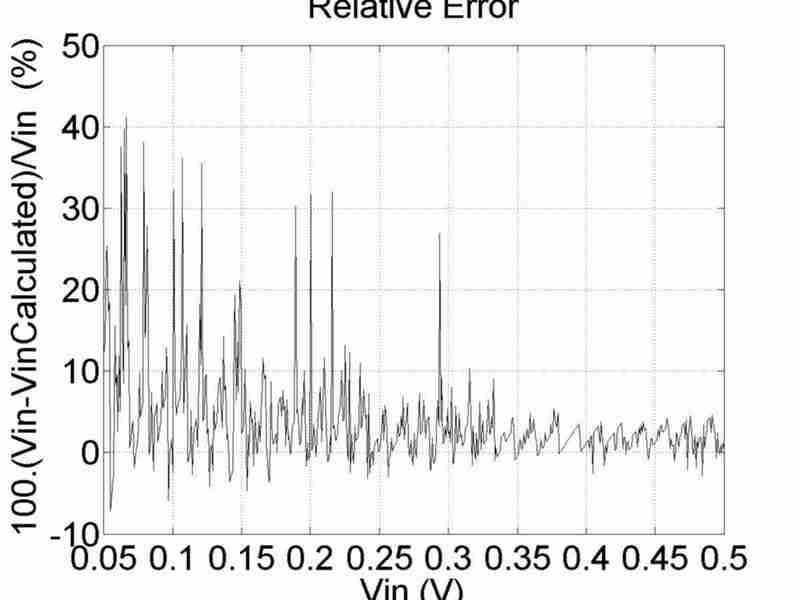

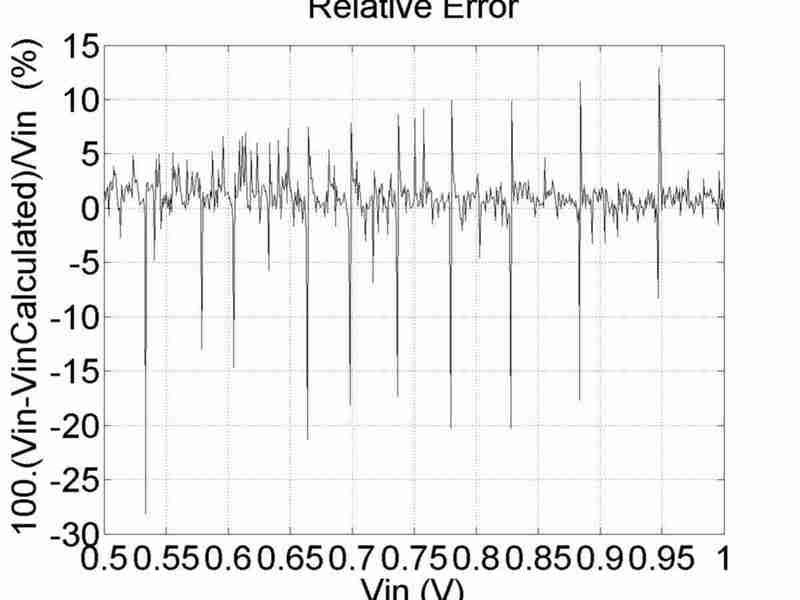

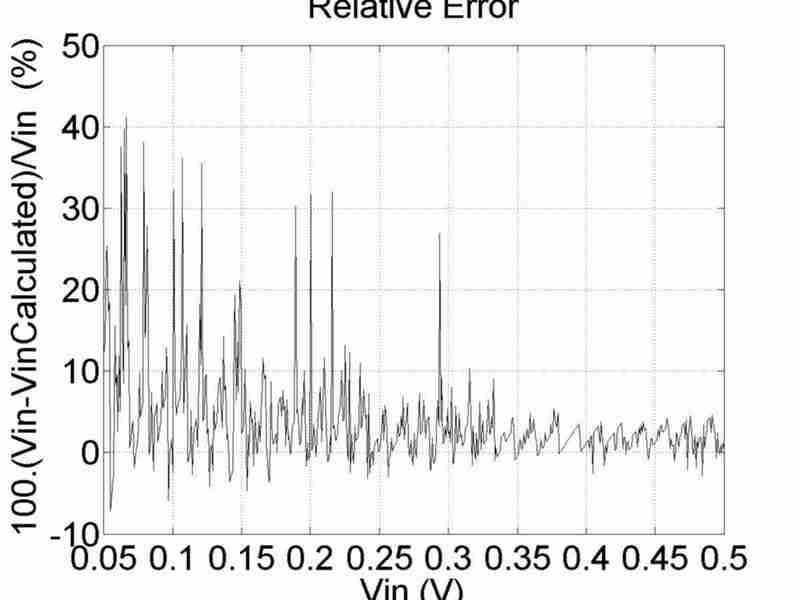

Um gráfico interessante que obtive, é o que fornece o erro relativo percentual da tensão de entrada Vin, com a tensão calculada VinCalculada, obtida via simulação computacional da conversão Delta-Sigma. Os erros são grandes porque o período de conversão é fixo, cerca de 1024 loops de 17 microsegundos. Isso acarreta que, ao final da conversão, o último ciclo na saída do comparador, não seja inteiramente monitorado.

Neste gráfico aparecem erros de quase 10 %, porém, quando se consideram mais pontos (valorers de Vin), aparecem maiores erros.

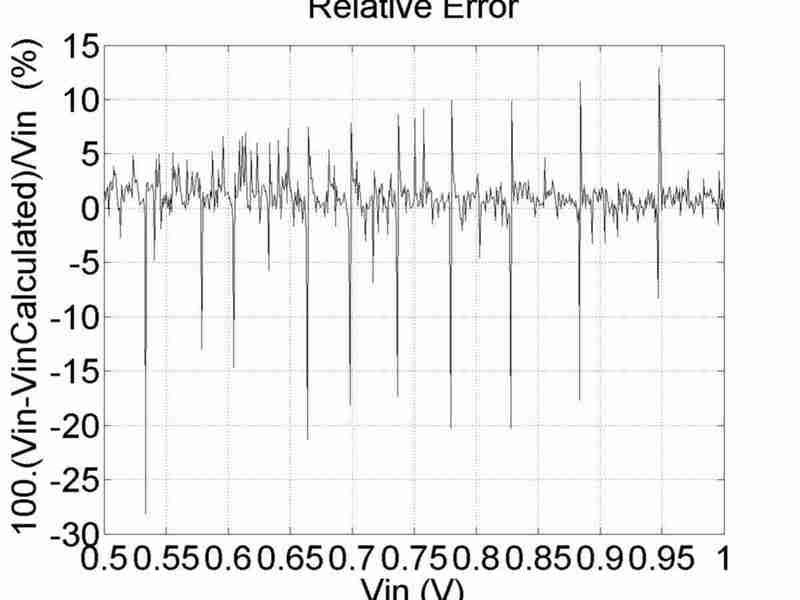

Neste gráfico tem-se mais pontos, porém, de valores diferentes do gráfico anterior.

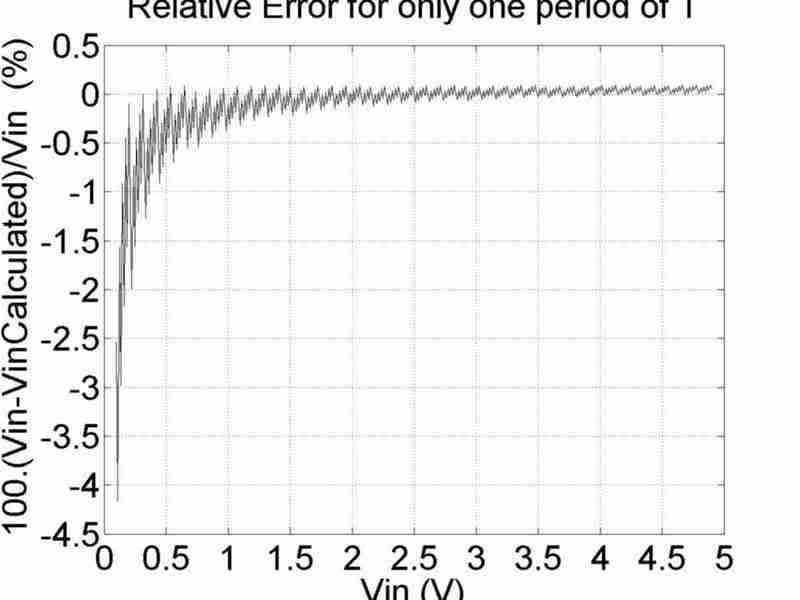

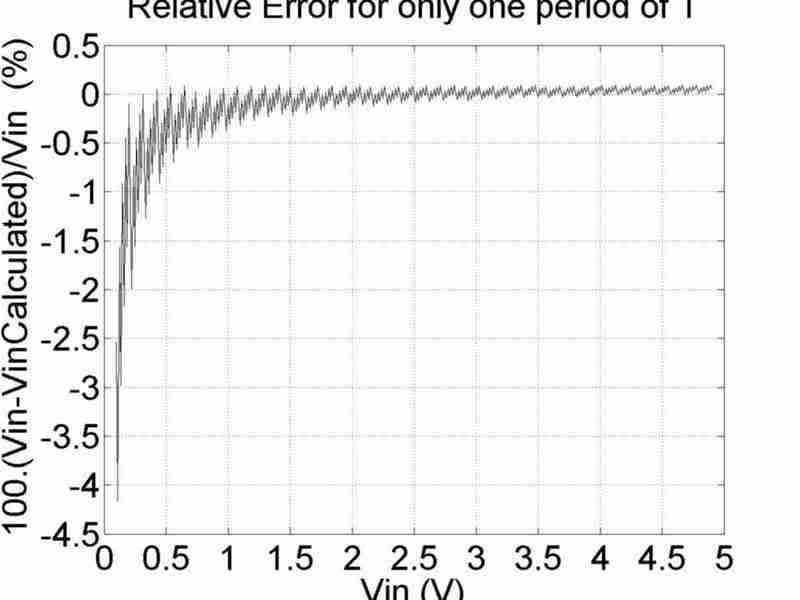

Neste gráfico a conversão se dá em apenas um ciclo do sinal na saída do comparador. Foi computado apenas para confirmar que, se a conversão ocorrer em um número inteiro de ciclos, o erro seria reduzido.

O ciclo (para cada valor da tensão de entrada) foi dividido em 1023 períodos iguais. Com um número inteiro de ciclos na conversão, o erro cai e tende para zero.

O erro ainda é grande na região inferior de Vin, devido ao fato de que o semi-período em zero lógico é muito pequeno em relação ao semi-período em um lógico. Não havendo sincronismo do instante da transição negativa (na saída do comparador) com os instantes de amostragem. O número de contagens durante o semi-período negativo pode variar de uma unidade. Uma variação pequena em um contador, que, neste caso, possuindo um número pequeno de contagens, fornece um erro grande.

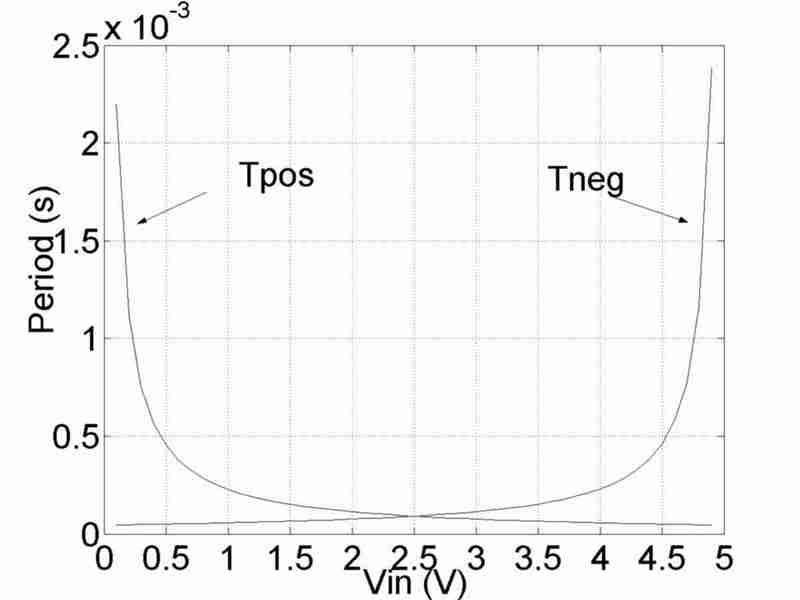

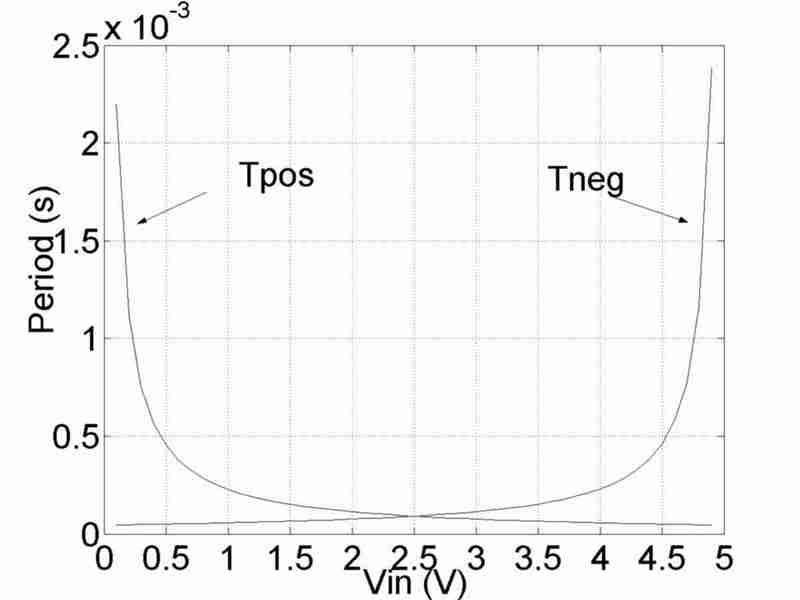

A seguir tem-se um gráfico que fornece os semi-períodos do ciclo na saída do comparador. Tpos para um lógico e Tneg para zero lógico. Os valores dos parâmetros foram:

Tensão máxima na saída para o resistor: 4,98 V.

Tensão mínima na saída para o resistor: 0,02 V.

Tensão de Referência: 2,5 V.

Resistor de entrada, junto à tensão desconhecida Vin: 47k Ohm

Resistor junto ao PIC: 47.569,7 Ohm. Valor calculado para que a relação entre a tensão Vin e Tneg/(Tneg + Tpos) seja linear e passe pela origem.

Capacitor: 100 nF.

Variação da tensão triangular sobre o capacitor: 0,05 V.

Período de amostragem (intervalo entre cada loop): 17 microsegundos.

Espero ter me feito entender. Sei que fica difícil em um espaço restrito. Algumas afirmações expostas pressupõem que já haja um prévio conhecimento do método exposto na AN-700.

Alguns gráficos possuem título em inglês. Apesar disso são originais. A explicação é que estou tentando expandir este estudo para tentar esclarecer minha hipótese. O texto em inglês acabou ficando mais claro que o texto em português. Estou contatando um colega para revisar a gramática, dadas as minhas limitações com esta língua.

Finalmente, não consegui postar uma imagem aqui, com um tamanho menor, sem perder totalmente suas informações. Peço que relevem este fato.

Grato.

MOR_AL

Caro Fábio. O assunto é interessante. Vislumbro duas maneiras de minimizar os erros apresentados adiante.

1- Caso fosse possível fazer uma conversão com um número inteiro de ciclos presentes na saída do comparador e que terminasse com um valor no contador de instantes monitorados (loops), que fosse fator de 2. Este sincronismo é praticamente impossível.

2- Outra possibilidade, esta menos impossível, seria fazer uma conversão com um número inteiro de ciclos e o contador de loops maior que 256. O problema é que seria necessário fazer uma divisão de números inteiros de até 16 bits (valor do registrador de número de eventos presentes no semi-ciclo negativo / valor do registrador de número de loops). Isso em um PIC com limitação de memória de programa seria difícil.

O circuito básico é mostrado na figura a seguir. Ela auxilia o acompanhamento dos fatores expostos.

Um gráfico interessante que obtive, é o que fornece o erro relativo percentual da tensão de entrada Vin, com a tensão calculada VinCalculada, obtida via simulação computacional da conversão Delta-Sigma. Os erros são grandes porque o período de conversão é fixo, cerca de 1024 loops de 17 microsegundos. Isso acarreta que, ao final da conversão, o último ciclo na saída do comparador, não seja inteiramente monitorado.

Neste gráfico aparecem erros de quase 10 %, porém, quando se consideram mais pontos (valorers de Vin), aparecem maiores erros.

Neste gráfico tem-se mais pontos, porém, de valores diferentes do gráfico anterior.

Neste gráfico a conversão se dá em apenas um ciclo do sinal na saída do comparador. Foi computado apenas para confirmar que, se a conversão ocorrer em um número inteiro de ciclos, o erro seria reduzido.

O ciclo (para cada valor da tensão de entrada) foi dividido em 1023 períodos iguais. Com um número inteiro de ciclos na conversão, o erro cai e tende para zero.

O erro ainda é grande na região inferior de Vin, devido ao fato de que o semi-período em zero lógico é muito pequeno em relação ao semi-período em um lógico. Não havendo sincronismo do instante da transição negativa (na saída do comparador) com os instantes de amostragem. O número de contagens durante o semi-período negativo pode variar de uma unidade. Uma variação pequena em um contador, que, neste caso, possuindo um número pequeno de contagens, fornece um erro grande.

A seguir tem-se um gráfico que fornece os semi-períodos do ciclo na saída do comparador. Tpos para um lógico e Tneg para zero lógico. Os valores dos parâmetros foram:

Tensão máxima na saída para o resistor: 4,98 V.

Tensão mínima na saída para o resistor: 0,02 V.

Tensão de Referência: 2,5 V.

Resistor de entrada, junto à tensão desconhecida Vin: 47k Ohm

Resistor junto ao PIC: 47.569,7 Ohm. Valor calculado para que a relação entre a tensão Vin e Tneg/(Tneg + Tpos) seja linear e passe pela origem.

Capacitor: 100 nF.

Variação da tensão triangular sobre o capacitor: 0,05 V.

Período de amostragem (intervalo entre cada loop): 17 microsegundos.

Espero ter me feito entender. Sei que fica difícil em um espaço restrito. Algumas afirmações expostas pressupõem que já haja um prévio conhecimento do método exposto na AN-700.

Alguns gráficos possuem título em inglês. Apesar disso são originais. A explicação é que estou tentando expandir este estudo para tentar esclarecer minha hipótese. O texto em inglês acabou ficando mais claro que o texto em português. Estou contatando um colega para revisar a gramática, dadas as minhas limitações com esta língua.

Finalmente, não consegui postar uma imagem aqui, com um tamanho menor, sem perder totalmente suas informações. Peço que relevem este fato.

Grato.

MOR_AL

-

MOR_AL - Dword

- Mensagens: 2940

- Registrado em: 19 Out 2006 09:38

- Localização: Rio de Janeiro - RJ

olá Kaoalex!

Seu nick é suspeito, KAO.....!

Mas, mesmo assim vou interceder por você!

O Fábio Pepeira é um bom garoto, gosta de ajudar, gosta de alavancar

os pensamentos , dá em suas obras pás para quem quiser aprender

construir seus castelos ( as plantas dos castelos, quem as conhecem

são usados nos alicercer- parecido com as antigas pirâmides).

Peço ao Fábio ( um grande colega de muito tempo!) que envie ao solicito o artigo em questão,pois sei que o mesmo solicito, vai adiquirí-lo em breve!!)

Uma "Amostra grátis", quem tem nome, quem tem honra, compra o que usa,... essa é idéia a passar, assim penso eu um humilde aprendiz!

Seu nick é suspeito, KAO.....!

Mas, mesmo assim vou interceder por você!

O Fábio Pepeira é um bom garoto, gosta de ajudar, gosta de alavancar

os pensamentos , dá em suas obras pás para quem quiser aprender

construir seus castelos ( as plantas dos castelos, quem as conhecem

são usados nos alicercer- parecido com as antigas pirâmides).

Peço ao Fábio ( um grande colega de muito tempo!) que envie ao solicito o artigo em questão,pois sei que o mesmo solicito, vai adiquirí-lo em breve!!)

Uma "Amostra grátis", quem tem nome, quem tem honra, compra o que usa,... essa é idéia a passar, assim penso eu um humilde aprendiz!

[]'s

Renie

-------------------------------------------------------------------------------------------------------------

Meu velho site com eletrônica praticamente parado http://www.reniemarquet.com

Nosso Blog http://artemadeiraevida.blogspot.com.br

Renie

-------------------------------------------------------------------------------------------------------------

Meu velho site com eletrônica praticamente parado http://www.reniemarquet.com

Nosso Blog http://artemadeiraevida.blogspot.com.br

- Renie

- Word

- Mensagens: 732

- Registrado em: 11 Out 2006 22:35

- Localização: RJ - Niterói - Brasil

Renie escreveu:olá Kaoalex!

Seu nick é suspeito, KAO.....!

Mas, mesmo assim vou interceder por você!

O Fábio Pepeira é um bom garoto, gosta de ajudar, gosta de alavancar

os pensamentos , dá em suas obras pás para quem quiser aprender

construir seus castelos ( as plantas dos castelos, quem as conhecem

são usados nos alicercer- parecido com as antigas pirâmides).

Peço ao Fábio ( um grande colega de muito tempo!) que envie ao solicito o artigo em questão,pois sei que o mesmo solicito, vai adiquirí-lo em breve!!)

Uma "Amostra grátis", quem tem nome, quem tem honra, compra o que usa,... essa é idéia a passar, assim penso eu um humilde aprendiz!

Ou então vá até a pagina da editora erica e faça o download,o link é:

http://download.editoraerica.com.br/pic ... quivos.exe

-

Jorge_Francisco - Dword

- Mensagens: 1009

- Registrado em: 12 Out 2006 09:53

- Localização: Rio de Janeiro

Valeu pela dica Jorge!

Renie,

Leia cao. Pode ficar tranquilo pq de Caô não tenho nada!

Infelizmente ainda não obtive sucesso no Proteus. A saída sempre está sendo igual a 5V. Será que estou errando em algo?

Thanks to PicTiger for providing Free Image Hosting.

Obrigado a todos pela ajuda

Renie,

Leia cao. Pode ficar tranquilo pq de Caô não tenho nada!

Infelizmente ainda não obtive sucesso no Proteus. A saída sempre está sendo igual a 5V. Será que estou errando em algo?

Thanks to PicTiger for providing Free Image Hosting.

Obrigado a todos pela ajuda

-

kaoalex - Byte

- Mensagens: 237

- Registrado em: 12 Out 2006 01:52

A página é a 322 ítem 12.8.2 Conversor A/D Delta - Sigma.

O exemplo é o 12.25 na página 325.

É só fazer o download do exemplo no link do livro no site da editora Érica.

Sdçs

O exemplo é o 12.25 na página 325.

É só fazer o download do exemplo no link do livro no site da editora Érica.

Sdçs

- Lorin

- Bit

- Mensagens: 31

- Registrado em: 13 Out 2006 18:44

sera que seria possivel no esquema do seguinte link usar os portos GP2 e GP3 na configuração de sigma delta

http://www.voti.nl/kitt-1/index_1.html

[ ] ' s

hw

http://www.voti.nl/kitt-1/index_1.html

[ ] ' s

hw

- net_hw

- Bit

- Mensagens: 10

- Registrado em: 24 Mar 2007 18:55

12 mensagens

• Página 1 de 1

Quem está online

Usuários navegando neste fórum: Nenhum usuário registrado e 1 visitante